Data Flow Modelling in Verilog

Jan 15 2020 Now Verilog code for full adder circuit with the behavioral style of modeling first demands the concept and working of a full adder. There are three types of modeling for Verilog.

Verilog Part 1 Example Dataflow And Structural Description Youtube

Verilog provides designers to design the devices based on different levels of abstraction that include.

. Dataflow modeling uses expressions instead of gates. Therefore data flow modeling is a very important way to use design. Assign couta.

While the gate-level and dataflow modeling are used for combinatorial circuits behavioral modeling is used for both sequential and combinatorial circuits. Verilog full adder in dataflow gate level modelling style. Dataflow modeling is a powerful approach to implement large circuit.

Up to 5 cash back Dataflow modeling provides a powerful way to implement a design. Half adder is a combinational arithmetic circuit that adds two numbers and produces a sum bit S and carry bit C as the output. Dataflow modeling describes hardware in terms of the flow of data from input to output.

Full Adder in Dataflow model. Iverilog is the Verilog compiler to run Verilog programs. A B and Cin.

The value assigned to the net is specified by an expression that uses operands and operators. Data flow modeling is therefore a very important way to use design. Dataflow modeling uses continuous assignments and the keyword assign.

What this means is you dont really need to know the circuit design. It is like connecting and arranging different parts of circuits available to implement a functions you are looking for. DATA FLOW AND RTL.

Examined the dataflow operators. Hi there I am trying to perform skin detection from an image in verilogThe image is of resolution 1200x900 ie contains 1080000 pixels. In verilog coding gate-level modeling works well due to the number of gates are less.

The logical expression for the two outputs sum and carry are given below. Compared to gate-level modeling data flow modeling in Verilog has a higher level of inaccessibility. Vvp is the command to run the Verilog code.

Continuous assignments are done using the keyword assign. Examined real-world effects under the dataflow model. What this means you do not really need to know the design of the circuit.

Gate Level Data Flow Switch Level and Behavioral modeling. Introduced and explored the Verilog dataflow or Register Transfer Level RTL model. - 9 of 9 -.

They are Dataflow Gate-level modeling and behavioral modeling. Dataflow modeling has become a well-liked design approach as logic synthesis tools became refined. Define expressions operators and operands.

In structural data flow modelling digital design functions are defined using components such as an invertor a MUX a adder a decoder basic digital logic gates etc. Dataflow style describes a system in terms of how data flows through the system. Hence dataflow modeling is a very important way of implementing the design.

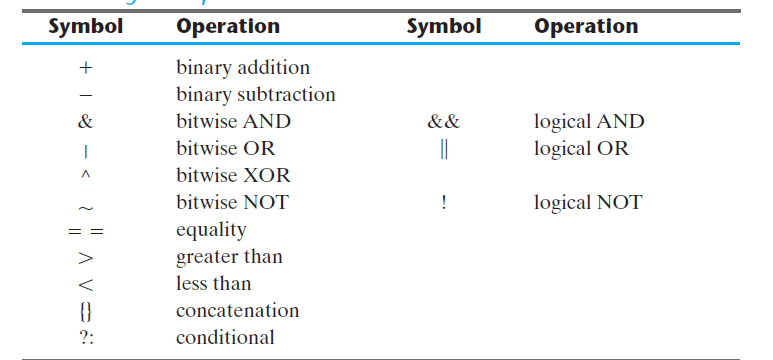

Verilog provides about 30 operator types. That really helps because modeling at the gate level becomes very difficult in a complex cycle. So if i want to describe a 2 to 4 decoder in dataflow modeling i would be like this.

Behavioral Model which is the highest level of abstraction Since we are using Behavioral Modeling we shall write the code using if-else to ensure the Priority. We need a boolean logic equation and ongoing allocation statements to build projects. Worked with the continuous assignment dataflow model.

Verilog allows a circuit to be designed in terms of the data flow between registers and how a design processes data rather than instantiation of individual gates. Developed Verilog dataflow level models of combinational and sequential circuits. A continuous assignment is a statement that assigns a value to a net.

Compared to gate-level modeling dataflow modeling in Verilog is a higher level of abstraction. Thats really helpful because gate-level modeling becomes very complicated for a complex circuit. Dataflow modeling utilizes Boolean equations and uses a number of operators that can acton inputs to produce outputs operators like -.

The datatype net is used in Verilog HDL to represent a physical connection between circuit elements. These tables list the supported Verilog HDL dataflow patterns that you can use when importing the HDL code. Dataflow modeling in Verilog allows a digital system to be designed in terms of its function.

The dataflow modeling style is mainly used to describe combinational circuits. In defining Data Flow Modeling a designer has to endure in mind how data flows within the design description. Data dependencies in the description match those in a typical hardware implementation.

You can then update the code as illustrated in the preceding examples. If your code uses an unsupported dataflow model such as code that infers a latch importhdl generates an error message with a link to the file name and line number. In this tutorial you will learn the data-flow modeling style of Verilog HDL Hardware Descriptive Language Objectives you will achieve after this tutorial.

A dataflow description directly implies a corresponding gate-level implementation. Dataflow modeling uses several operators that act on operands to produce the desired results. Explain assignment delay implicit assignment delay and net declaration delay for continuous assignment statements.

If large number of gates are used in a circuit then this type of modeling will be complicated. Dataflow descriptions consist of one or more concurrent signal assignment statements. Verilog Language is a very famous and widely used programming language to design digital IC In this verilog tutorial level of abstraction has been covered.

Module fulladder input a input b input cin output s output cout.

What Is The Difference Between Data Flow And Behavioral Modelling In Verilog Hdl Ee Vibes

Veriloghdl Basic Data Flow Modelling Youtube

Lecture 4 Dataflow And Behavioral Modeling I Youtube

Data Flow Modeling Verilog Hdl Lecture Slides Slides Verilog And Vhdl Docsity

Comments

Post a Comment